@ExecutableFix 和 @Greymon55,剛剛在 Twitter 上分享了與 AMD 下一代 Zen 5 霄龍(EPYC)Turin 處理器有關的一些有趣細節。據說作為 Genoa 系列的繼任者,EPYC Turin 將沿用 SP5 平臺,輔以前所未見的封裝設計。今年晚些時候,我們有望率先在 EPYC Milan-X 上見到堆疊式 3D 小晶片設計的演變。

當 AMD霄龍 Turin 處理器在數年後正式亮相時,可推測該系列晶片將在一塊基板上整合多個 CCD 與快取堆疊。

相比之下,Genoa CPU 最高擁有 96 個核心,而 Bergamo 算是在同一 Zen 4 架構上的演進版本,據說擁有最高 128 個核心。

除了 CPU 與快取設計,傳聞還稱 Turing 還有望迎來 256 個核心、且搭配 PCIe 6.0 。若 AMD 有意採用堆疊式 X3D 小晶片方案,甚至可以推到更高。

至於如何在相同的 SP5 平臺上容納兩倍於 Genoa / Bergamo 的核心數量,我們對傳說中的 192C / 384T 和 256C / 512T 的 EPYC Turin CPU 還是充滿了好奇。

預計為了實現這一目標,AMD 有兩條技術路線可選。其一是讓每個 CCD 的核心數翻倍,目前 Zen 3 / Zen 4 的單 CCD 可容納 8 個核心。

若翻倍到單 CCD / 16 個核心,最終 EPYC 伺服器處理器有望透過堆疊 12 / 16 個 CCD,達成 192 / 256 個核心的目的。

在早前的傳聞中,MLID 了一種全新的封裝佈局,即在 SP5 平臺上可支援多達 16 組 CCD 。不過 AMD 還有另一條可能性較低的技術路線,那就是在 CCD 之上繼續堆疊 CCD 。

如此以來,即便每組 CCD 維持 8 個核心不變,總體設計還是可以達成多晶片 / 16 組 CCD 。

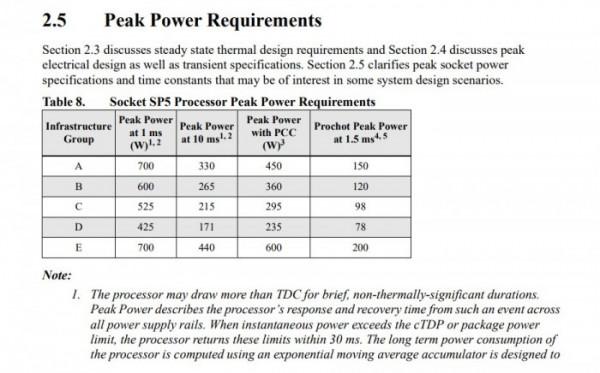

至於晶片的熱設計功耗(TDP),即使 EPYC Turin 用上臺積電最先進的 3nm 工藝製程,雙倍核心的功率需求也是相當誇張的。

即將推出的 96 核 EPYC Genoa CPU,其可調 cTDP 已經高達 400W 。若 EPCY Turin 的 cTDP 最高衝擊到了 600W,SP5 插槽(LGA 6096)似乎也可承受 700W 的峰值功耗(雖然只能持續 1ms)。

Gigabyte 的洩露資料已證實有關下一代平臺的各種資訊,可知 SP5 針腳數量比當前的 LGA 4094 還多了 2002 個觸點。

如果將持續時間放寬到 10ms,那 SP5 平臺的峰值功率將落到 440W(OCC 峰值 600W)。在超過 cTDP 之後,EPYC 晶片將在 30ms 內恢復限制。

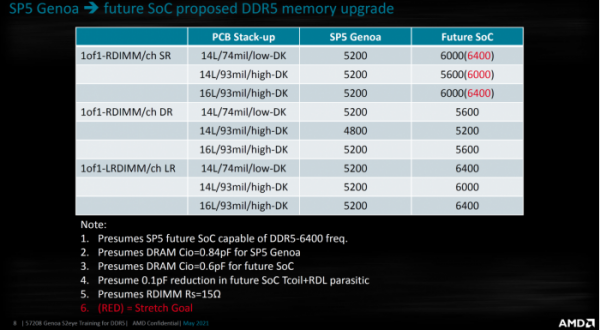

最後,洩露的 AMD 簡報還證實了 EPYC Genoa 繼任者的 SoC 將支援更高的 DDR5-6000 到 6400 記憶體(或指代 Bergamo / Turin)。

如果一切順利,AMD 或於 2024 - 2025 年左右推出 EPYC Turin,並將與英特爾的 Diamond Rapids Xeon 平臺展開更直接的競爭。